LV16-24-FSMC-01-外部SRAM基础

本文主要是STM32开发——外部SRAM的一些相关笔记,若笔记中有错误或者不合适的地方,欢迎批评指正😃。

点击查看使用工具及版本

| Windows | windows11 |

| Ubuntu | Ubuntu16.04的64位版本 |

| VMware® Workstation 16 Pro | 16.2.3 build-19376536 |

| SecureCRT | Version 8.7.2 (x64 build 2214) - 正式版-2020年5月14日 |

| 开发板 | 正点原子 i.MX6ULL Linux阿尔法开发板 |

| uboot | NXP官方提供的uboot,NXP提供的版本为uboot-imx-rel_imx_4.1.15_2.1.0_ga(使用的uboot版本为U-Boot 2016.03) |

| linux内核 | linux-4.15(NXP官方提供) |

| STM32开发板 | 正点原子战舰V3(STM32F103ZET6) |

点击查看本文参考资料

- 通用

| 分类 | 网址 | 说明 |

| 官方网站 | https://www.arm.com/ | ARM官方网站,在这里我们可以找到Cotex-Mx以及ARMVx的一些文档 |

| https://www.st.com/content/st_com/zh.html | ST官方网站,在这里我们可以找到STM32的相关文档 | |

| https://www.stmcu.com.cn/ | 意法半导体ST中文官方网站,在这里我们可以找到STM32的相关中文参考文档 | |

| http://elm-chan.org/fsw/ff/00index_e.html | FatFs文件系统官网 | |

| 教程书籍 | 《ARM Cortex-M3权威指南》 | ARM公司专家Joseph Yiu(姚文祥)的力作,中文翻译是NXP的宋岩 |

| 《ARM Cortex-M0权威指南》 | ||

| 《ARM Cortex-M3与Cortex-M4权威指南》 | ||

| 开发论坛 | http://47.111.11.73/forum.php | 开源电子网,正点原子的资料下载及问题讨论论坛 |

| https://www.firebbs.cn/forum.php | 国内Kinetis开发板-野火/秉火(刘火良)主持的论坛,现也做STM32和i.MX RT | |

| https://www.amobbs.com/index.php | 阿莫(莫进明)主持的论坛,号称国内最早最火的电子论坛,以交流Atmel AVR系列单片机起家,现已拓展到嵌入式全平台,其STM32系列帖子有70W+。 | |

| http://download.100ask.net/index.html | 韦东山嵌入式资料中心,有些STM32和linux的相关资料也可以来这里找。 | |

| 博客参考 | http://www.openedv.com/ | 开源网-原子哥个人博客 |

| http://blog.chinaaet.com/jihceng0622 | 博主是原Freescale现NXP的现场应用工程师 | |

| cortex-m-resources | 这其实并不算是一个博客,这是ARM公司专家Joseph Yiu收集整理的所有对开发者有用的官方Cortex-M资料链接(也包含极少数外部资源链接) |

- STM32

| STM32 | STM32 HAL库开发实战指南——基于F103系列开发板 | 野火STM32开发教程在线文档 |

| STM32库开发实战指南——基于野火霸道开发板 | 野火STM32开发教程在线文档 |

- SD卡

| SD Association | 提供了SD存储卡和SDIO卡系统规范 |

点击查看相关文件下载

| STM32F103xx英文数据手册 | STM32F103xC/D/E系列的英文数据手册 |

| STM32F103xx中文数据手册 | STM32F103xC/D/E系列的中文数据手册 |

| STM32F10xxx英文参考手册(RM0008) | STM32F10xxx系列的英文参考手册 |

| STM32F10xxx中文参考手册(RM0008) | STM32F10xxx系列的中文参考手册 |

| Arm Cortex-M3 处理器技术参考手册-英文版 | Cortex-M3技术参考手册-英文版 |

| STM32F10xxx Cortex-M3编程手册-英文版(PM0056) | STM32F10xxx/20xxx/21xxx/L1xxxx系列Cortex-M3编程手册-英文版 |

| SD卡相关资料——最新版本 | 有关SD卡的一些资料可以从这里下载 |

| SD卡相关资料——历史版本 | 有关SD卡的一些历史版本资料可以从这里下载,比如后边看的SD卡2.0协议 |

| SD 2.0 协议标准完整版 | 这是一篇关于SD卡2.0协议的中文文档,还是比较有参考价值的,可以一看 |

STM32F103ZET6 自带了 64K 字节的 SRAM,对一般应用来说,已经足够了,不过在一些对内存要求高的场合, STM32F1 自带的这些内存就不够用了。比如跑算法或者跑 GUI 等,就可能不太够用,所以战舰 STM32F103 板载了一颗 1M 字节容量的 SRAM 芯片: IS62WV51216,满足大内存使用的需求。 注意:笔记中有一些 # 表示低电平有效,知识横线不好打,就用#代替了。

一、为什么要扩展SRAM?

STM32控制器芯片内部有一定大小的SRAM及FLASH作为内存和程序存储空间,程序下载的时候是存放在内部的FLASH中的,在程序运行过程中,会有一些变量或者其他的东西存放在SRAM中运行,这就跟我们PC电脑上的内存一样。当程序较大,内存和程序空间不足时,就需要在STM32芯片的外部扩展存储器了。STM32F103ZE系列芯片可以扩展外部SRAM用作内存。

给STM32芯片扩展内存与给PC扩展内存的原理是一样的,只是PC上一般以内存条的形式扩展,而且内存条实质是由多个内存颗粒(即SDRAM芯片)组成的通用标准模块,而STM32扩展时,直接直接与SRAM芯片连接。

一、XM8A51216

1. 简介

XM8A51216 是深圳星忆存储科技有限公司(星忆存储 )生产的一颗 16 位宽 512K(512*16,即 1M 字节)容量的 CMOS 静态内存芯片。我们可以在这里找到它的芯片手册:。该芯片具有如下几个特点 :

(1)高速。 具有最高访问速度 10/12ns。

(2)低功耗。

(3)TTL 电平兼容。

(4)全静态操作。不需要刷新和时钟电路。

(5)三态输出。

(6)字节控制功能。支持高/低字节控制。

2. 功能框图

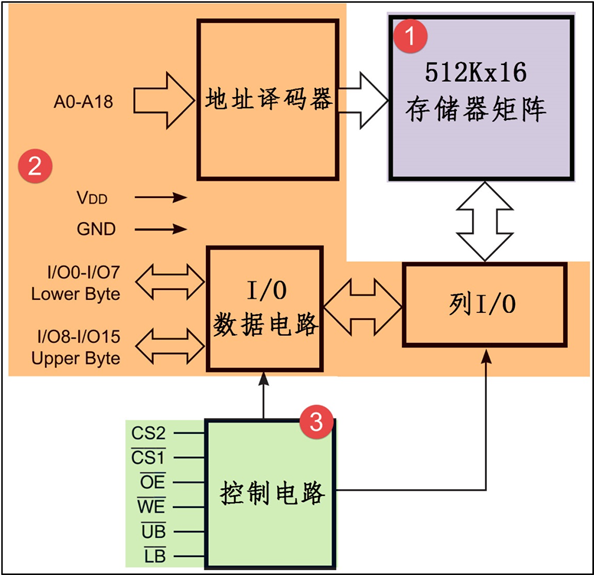

功能框图我们可以看 XM8A51216V33(8M).pdf (xingmem.com) 的 Logic Block Diagram:

图中 A018 为地址线,总共 19 根地址线(即 2^19=512K, 1K=1024); DQ015 为数据线,总共 16 根数据线。 CEn 是芯片使能信号,低电平有效; OEn 是输出使能信号,低电平有效;WEn 是写使能信号,低电平有效; BLEn 和 BHEn 分别是高字节控制和低字节控制信号;

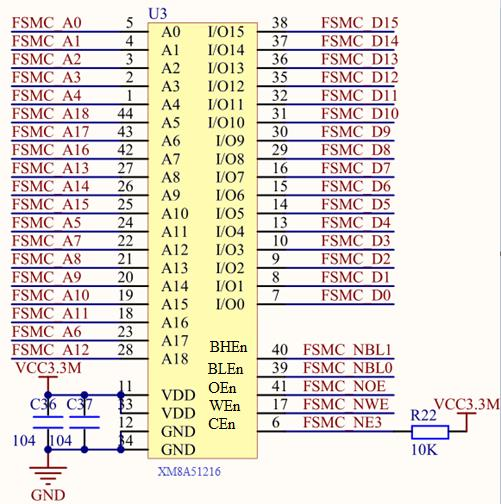

3. 与STM32接线

战舰 STM32F103 使用的是 TSOP44 封装的 XM8A51216 芯片,该芯片直接接在 STM32F1的 FSMC 上,

从原理图可以看出, XM8A51216 同 STM32F1 的连接关系:

1 | A[0:18]--->FMSC_A[0:18](不过顺序错乱了) |

XM8A51216 的 A[0:18]并不是按顺序连接 STM32F1 的 FMSC_A[0:18],不过这并不影响我们正常使用外部 SRAM,因为地址具有唯一性。所以,只要地址线不和数据线混淆,就可以正常使用外部 SRAM。这样设计的好处,就是可以方便 PCB 布线。 什么事FSMC?我们后边再说。

二、IS62WV51216

为什么还有这个?因为教程中是XM8A51216,但是实际我使用的板子的芯片是 IS62WV51216。

1. 简介

IS62WV51216是ISSI(Integrated Silicon Solution, Inc)公司生产的一颗16位宽512K(512*16,即1M字节)容量的CMOS静态内存(SRAM)芯片。开发板上使用的完整的型号是 IS62WV51216BLL,它有以下特点:

(1)高速。具有45ns/55ns访问速度。

(2)低功耗。操作时:36mW;待机时:12uW。

(3)兼容TTL电平。

(4)全静态操作。不需要刷新和时钟电路。

(5)三态输出。

(6)字节控制功能。支持高/低字节控制。

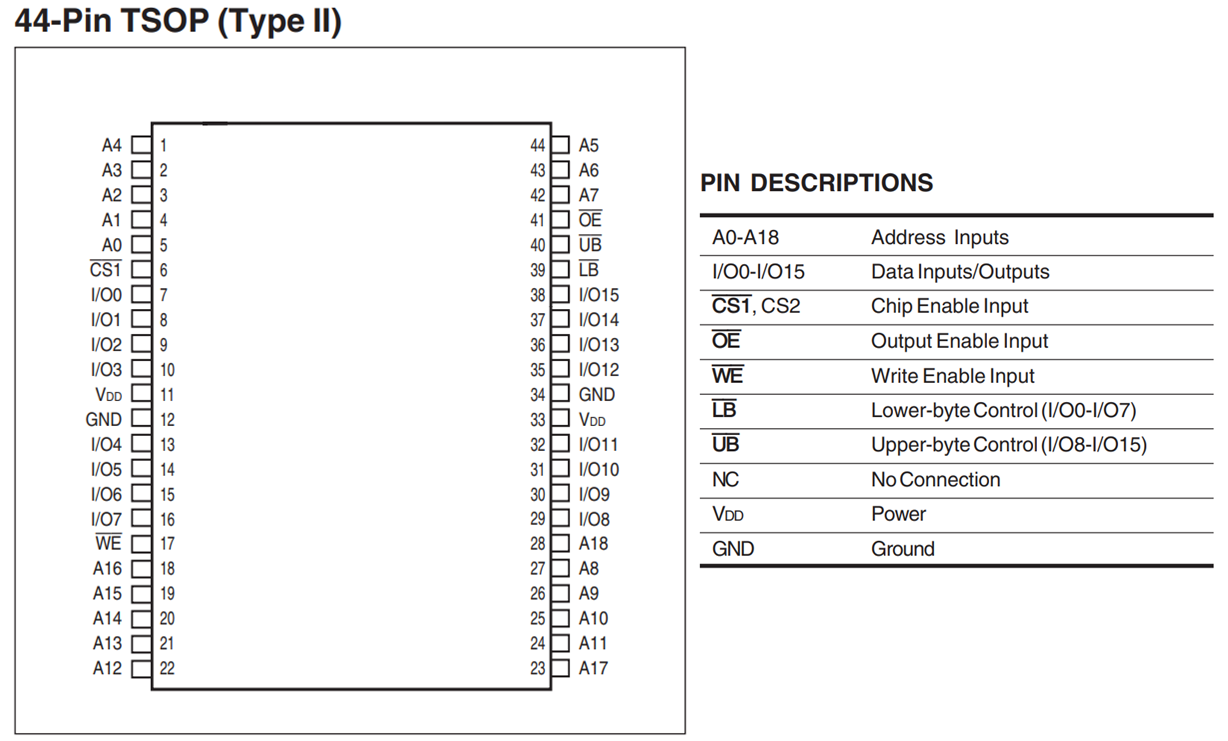

2. 引脚说明

各个引脚的说明如下图表(表中的#就表示图中的字母上方的横线,表示低电平有效):

| 信号线 | 类型 | 说明 |

|---|---|---|

| A0-A18 | I | 地址输入 |

| I/O0-I/O7 | I/O | 数据输入输出信号,低字节 |

| I/O8-I/O15 | I/O | 数据输入输出信号,高字节 |

| CS2 和CS1# | I | 片选信号,CS2高电平有效,CS1#低电平有效,部分芯片只有其中一个引脚 |

| OE# | I | 输出使能信号,低电平有效 |

| WE# | I | 写入使能信号,低电平有效 |

| UB# | I | 数据掩码信号Upper Byte,高位字节允许访问,低电平有效, |

| LB# | I | 数据掩码信号Lower Byte,低位字节允许访问,低电平有效 |

SRAM的控制比较简单,只要控制信号线使能了访问,从地址线输入要访问的地址,即可从I/O数据线写入或读出数据。

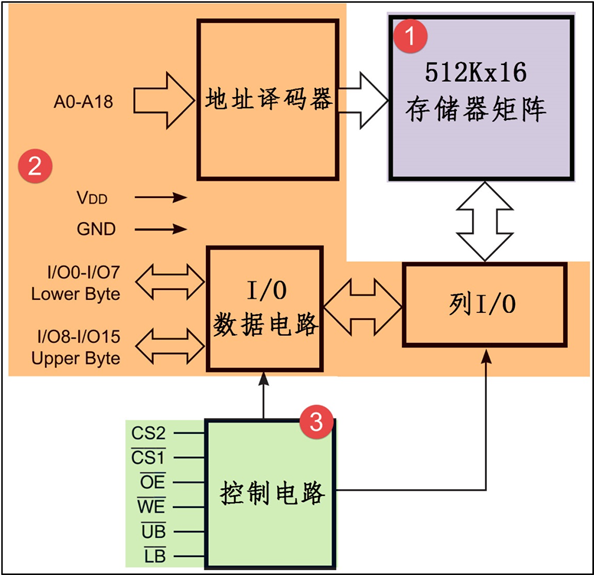

3. 功能框图

功能框图我们可以看IS62WV51216BLL-datasheet的 FUNCTIONAL BLOCK DIAGRAM部分:

3.1 ①存储器矩阵

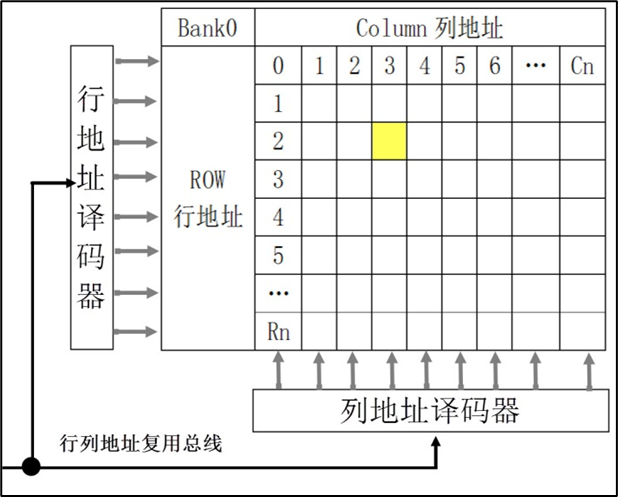

SRAM的存储矩阵如下图所示:

SRAM内部包含的存储阵列,可以把它理解成一张表格,数据就填在这张表格上。和表格查找一样,指定一个行地址和列地址,就可以精确地找到目标单元格,这是SRAM芯片寻址的基本原理。这样的每个单元格被称为存储单元,而这样的表则被称为存储矩阵。

3.2 ②地址译码器、列I/O和I/O数据电路

地址译码器把N根地址线转换成2N根信号线,每根信号线对应一行或一列存储单元,通过地址线找到具体的存储单元,实现寻址。如果存储阵列比较大,地址线会分成行和列地址,或者行、列分时复用同一地址总线,访问数据寻址时先用地址线传输行地址再传输列地址。

我们使用的这个的SRAM比较小,没有列地址线,它的数据宽度为16位,即一个行地址对应2字节空间,框图中左侧的A0-A18是行址信号(共19根),当有18根地址线一共可以表示$2^{18}=2^8*1024=512K$行存储单元,所以18根地址线一共能访问512Kx16bits大小的空间,一共就是512K*2B=1024KB=1MB,刚好就是1M字节的大小,所以其实实际上我们使用18根地址线就足够了。访问时,使用UB#或LB#线控制数据宽度。

我们每次给一个18位的地址,这会对应一个16位的数据空间,比如我们给了一个0地址,这个时候我们可以访问16位的数据:

| 地址 | 0~7位 | 8~15位 |

|---|---|---|

| 0 | xxxx xxxx | xxxx xxxx |

| 1 | xxxx xxxx | xxxx xxxx |

可以访问到第0字节和第1字节的数据,那么怎么确定访问的是第0字节还是第1字节呢?我们这个时候将这两个字节的07位看做低8位,对应I/O0I/O7,815位看做高8位,对应I/O8I/O15,然后通过UB#或LB#线来控制是要访问高位还是低位,UB#控制的是高字节的访问,LB#控制低字节的访问:

| LB# | UB# | 有效的数据线 |

|---|---|---|

| 低电平 | 高电平 | I/O0~I/O7,此时可访问低8位 |

| 高电平 | 低电平 | I/O8~I/O15,此时可访问低8位 |

| 低电平 | 低电平 | I/O0 |

| 高电平 | 高电平 | 均无效,无法访问数据 |

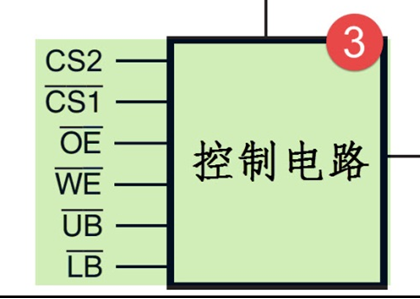

3.3 ③控制电路

控制电路主要包含了片选、读写使能以及上面提到的宽度控制信号UB#和LB#。利用CS2或CS1#片选信号,可以把多个SRAM芯片组成一个大容量的内存条。OE#和WE#可以控制读写使能,防止误操作。

访问时,使用 UB# 或 LB# 线控制数据宽度,例如,当要访问宽度为 16 位的数据时,使用行地址线指出地址,然后把 UB# 和 LB# 线都设置为低电平,那么 I/O0-I/O15 线都有效,它们一起输出该地址的 16 位数据 (或者接收 16 位数据到该地址);当要访问宽度为 8 位的数据时,使用行地址线指出地址,然后把UB# 或 LB# 其中一个设置为低电平,I/O 会对应输出该地址的高 8 位和低 8 位数据,因此它们被称为数据掩码信号。

3. 读写时序

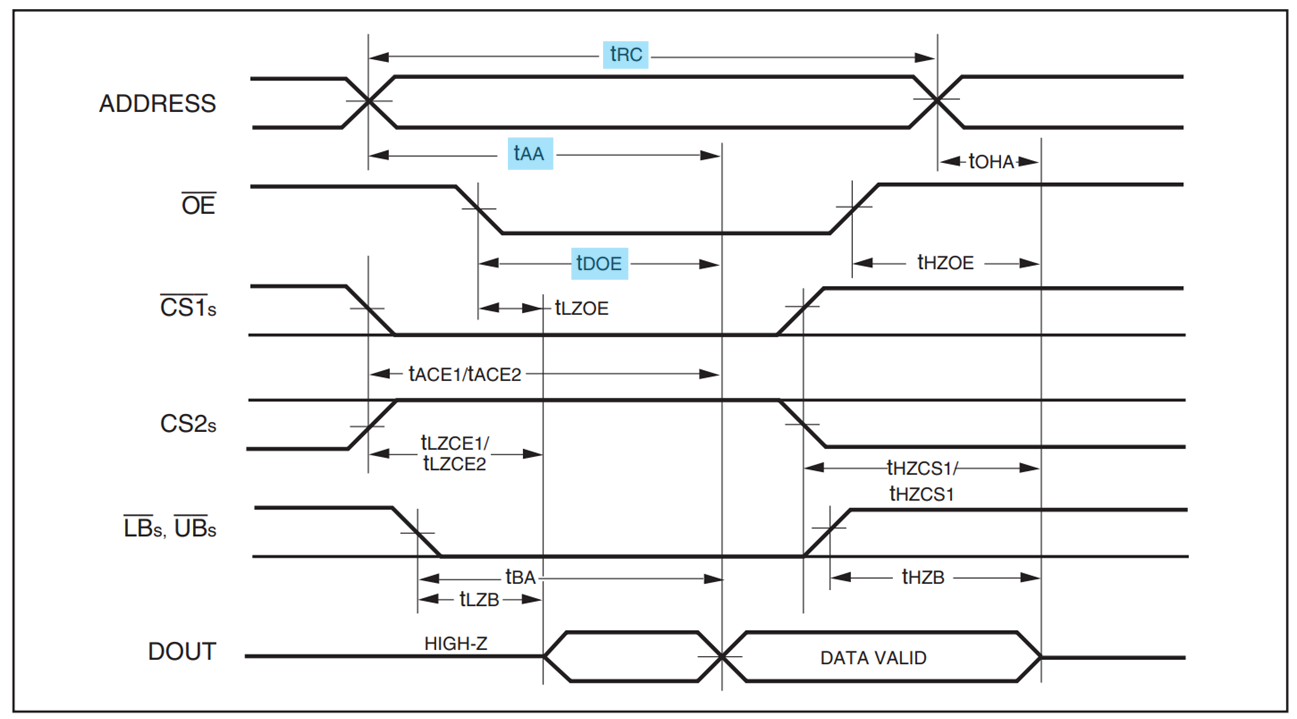

注意,下边的时序图都是没有时钟线的,这也说明SRAM是通过异步通信的方式进行读写的。

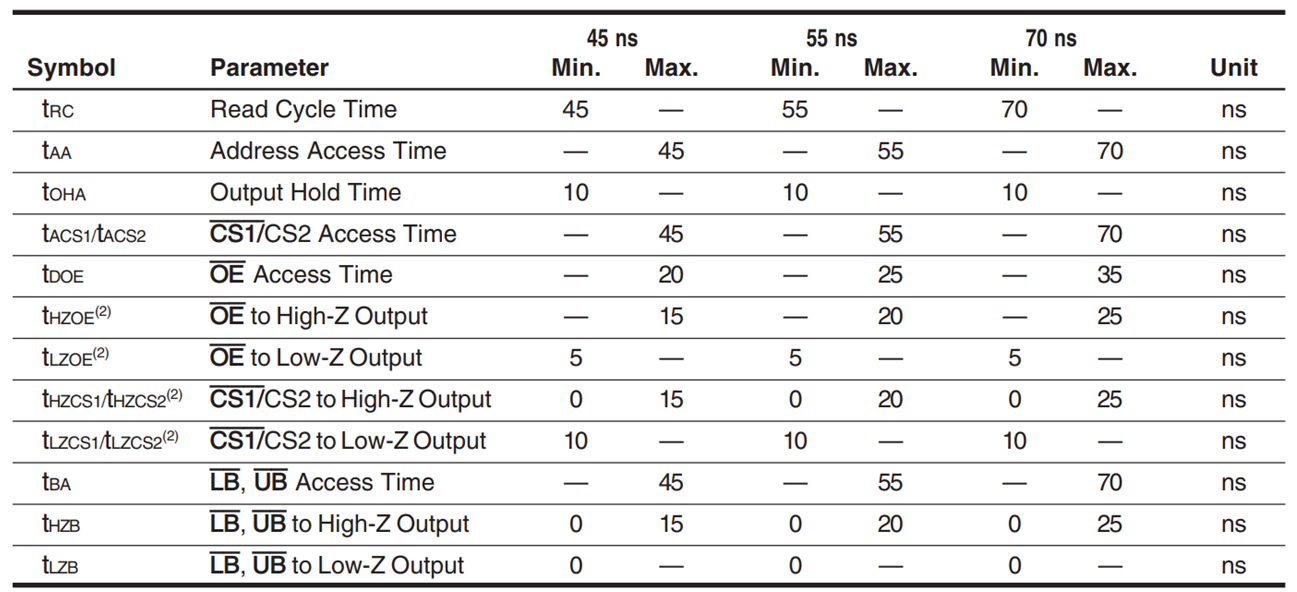

3.1 读时序

上图为IS62WV51216芯片的8080并口读时序,我们重点要关注的是:读周期时间(tRC)、地址建立时间(tAA)和OE建立时间(tDOE)。开发板使用55ns的IS62WV51216,tRC=55ns,tAA=55ns(Max),tDOE=25ns(Max):

读时序过程:

(1)主机使用地址信号线发出要访问的存储器目标地址;

(2)控制片选信号CS1#及CS2#使能存储器芯片;

(3)控制读使能信号OE#表示要读数据;

(4)使用掩码信号LB#与UB#指示要访问目标地址的高、低字节部分;

(5)存储器会通过数据线向主机输出目标数据。

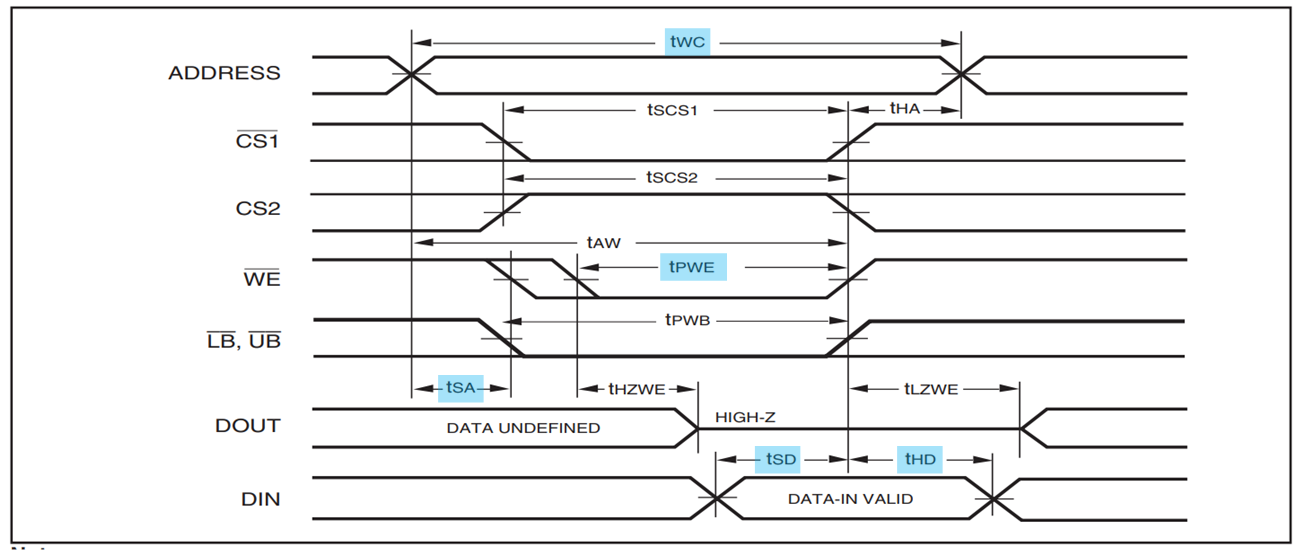

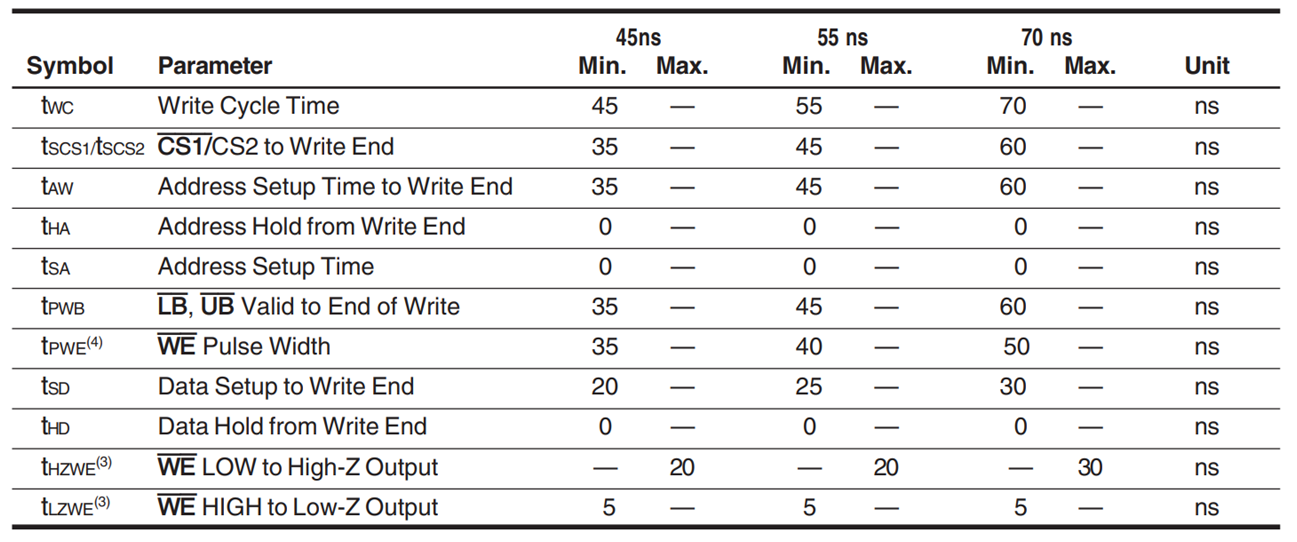

3.2 写时序

上图为IS62WV51216芯片的8080并口写时序,我们重点要关注的是:读周期时间(tWC)、地址建立时间(tSA)和OE建立时间(tPWE)。开发板使用55ns的IS62WV51216,tWC=55ns,tSA=0ns,tPWE=45ns(min):

写时序过程:

(1)主机使用地址信号线发出要访问的存储器目标地址;

(2)控制片选信号CS1#及CS2#使能存储器芯片;

(3)控制写使能信号WE#表示要写数据;

(4)使用掩码信号LB#与UB#指示要访问目标地址的高、低字节部分;

(5)使用数据线向存储器传输目标数据。

3.3 关键时间参数总结

| 时间参数 | IS62WV51216BLL-55ns 型号要求的最短时间 |

说明 |

|---|---|---|

| tRC | 55ns | 读操作周期 |

| tAA | 0ns | 地址访问时间 |

| tWC | 55ns | 写操作周期 |

| tSA | 0ns | 地址建立时间 |

| tSD | 25ns | 数据建立至写结束的时间 |

| tHD | 0ns | 数据写结束后的保持时间 |

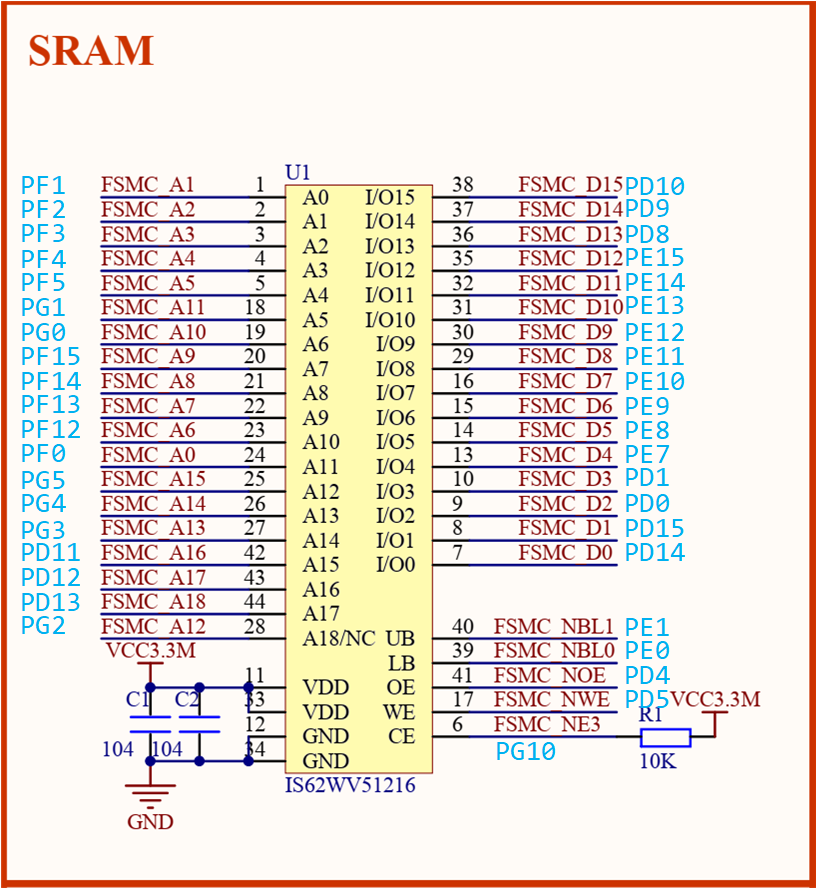

4. 与STM32接线

理论上IS62WV51216与STM32的FSMC接线应该是这样的:

1 | A[0:18]--->FMSC_A[0:18] |

实际上IS62WV51216 的 A[0:18]并不是按顺序连接 STM32F1 的 FMSC_A[0:18],不过这并不影响我们正常使用外部 SRAM,因为地址具有唯一性。所以,只要地址线不和数据线混淆,就可以正常使用外部 SRAM。这样设计的好处,就是可以方便 PCB 布线。

三、怎么驱动?

上边了解了那么多,那怎么使用SRAM呢?当然是通过STM32的FSMC来驱动啦,FSMC是啥?我们在下一篇笔记中学习。